RTOS für Middleware auf Cortex-M

Format: Online-Schulung

Dauer: 2 Tage, jeweils von 9 Uhr – 13 Uhr.

Kurssprache: Deutsch (Präsentationsfolien auf Englisch)

Preis: 650,00 EUR (Frühbucher-Rabatt 100,- EUR)

SAFERTOS® ist ein vorzertifiziertes Sicherheits-Echtzeitbetriebssystem (RTOS), das von WHIS, einem Unternehmen für Sicherheitssysteme, entwickelt wurde. Es bietet überragende Leistung und vorzertifizierte Zuverlässigkeit bei minimalem Ressourcenverbrauch. Es basiert auf dem FreeRTOS-Funktionsmodell, mit einfachen Migrationsmöglichkeiten. SAFERTOS ist vom TÜV SÜD vorzertifiziert nach IEC 61508-3 SIL 3 oder vom TÜV SÜD vorzertifiziert nach ISO 26262 ASIL D erhältlich.

Mit einer kaum wahrnehmbaren Anlaufzeit ist SAFERTOS die ideale Wahl für Systeme, die nach einem Stromausfall oder einer Unterbrechung der Stromversorgung Personen und Anlagen schnell vor Gefahren schützen müssen.

SAFERTOS bietet eine deterministische Ereignisverarbeitung, die häufig in Motorsteuerungsanwendungen eingesetzt wird, die eine präzise Steuerung erfordern. Es ist die ideale Wahl für Systeme, die schnell auf sicherheitsrelevante Ereignisse reagieren und das System in kürzester Zeit in einen sicheren Zustand bringen müssen.

Es ist üblich, den Stromverbrauch des Prozessors zu reduzieren, indem der Idle-Task-Hook verwendet wird, um den Prozessor in einen Stromsparmodus zu versetzen. Die mit dieser einfachen Methode erreichbare Energieeinsparung variiert je nach CPU-Auslastung, wird aber durch die Notwendigkeit begrenzt, den Energiesparmodus regelmäßig zu verlassen und wieder zu aktivieren, um RTOS-Tick-Interrupts zu verarbeiten.

Alternativ kann SAFERTOS verwendet werden, wenn es vom Prozessor unterstützt wird und einen Ultra-Low-Power-Modus ohne Ticks unterstützt. In diesem Modus wird Strom gespart, indem der RTOS-Tick-Interrupt während Leerlaufzeiten vollständig gestoppt und das System in einen Energiesparmodus versetzt wird. Durch das Stoppen des Tick-Interrupts kann der Prozessor länger in einem Stromsparmodus verbleiben, bis entweder ein Interrupt auftritt oder das RTOS eine Task wieder aktiviert.

Ein RTOS, das dynamische Speicherzuweisungen durchführt, kann ein erhebliches Risiko für ein sicherheitskritisches System darstellen. Was passiert, wenn das RTOS mehr Speicher zuweisen muss, um eine Sicherheitstask auszuführen, aber kein Speicher mehr verfügbar ist?

SAFERTOS führt keine dynamische Speicherzuweisung durch, sondern erfordert, dass die Anwendung während der Initialisierungssequenz einen Speicherblock für SAFERTOS reserviert. Die Referenz auf diesen Speicherblock wird SAFERTOS während der Initialisierungsphase über die API übergeben. Anwendungsentwickler können weiterhin die dynamische Speicherzuweisung in ihren Designs verwenden.

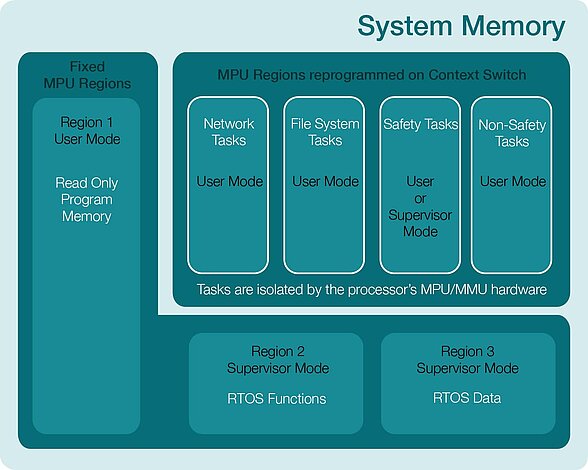

SAFERTOS unterstützt die Definition und Bearbeitung von MPU-Regionen auf Aufgabenbasis. Diese Funktion stellt die Tools bereit, mit denen Entwickler eine gewisse räumliche Trennung zwischen Aufgaben hinzufügen können. Bei effektiver Verwendung kann verhindert werden, dass Aufgaben direkt unbeabsichtigt oder versehentlich auf falsche Speicherbereiche zugreifen.

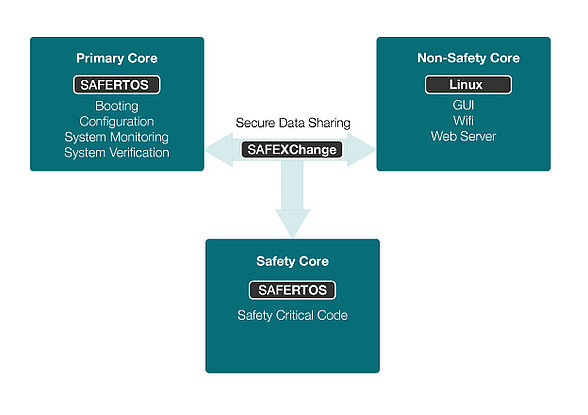

SAFERTOS ist ideal für den Einsatz auf dem Boot-Kern eines Multicore-/Multiprozessor-Sicherheitssystems geeignet. SAFERTOS kann das System schnell und effektiv hochfahren, die Sicherheitspartitionen konfigurieren und kritische Sicherheitsfunktionen ausführen, bevor andere Kerne/Prozessoren aktiviert werden, auf denen unkritische Anwendungen wie Linux ausgeführt werden könnten, um Webserver und WLAN-Verbindungen zu implementieren.

In einer Multicore-Umgebung wird SAFERTOS typischerweise auf Kernen verwendet, die sicherheitskritische Funktionen implementieren, oder auf Kernen, die die Überwachung/Verifizierung der Primärfunktion ermöglichen. Aufgrund seiner hohen Sicherheitsklassifizierung kann SAFERTOS sicher sowohl auf Primär- als auch auf Überwachungskernen verwendet werden, sodass keine Differenzierungssoftware erforderlich ist.

Format: Online-Schulung

Dauer: 2 Tage, jeweils von 9 Uhr – 13 Uhr.

Kurssprache: Deutsch (Präsentationsfolien auf Englisch)

Preis: 650,00 EUR (Frühbucher-Rabatt 100,- EUR)