RTOS for Middleware for Cortex-M

Format: online training

Duration: 2 days, from 9:00 a.m. to 1 p.m.

Language of instruction: German (presentation slides in English)

Costs: 650.00 EUR (early bird discount 100 EUR)

SAFERTOS® is a pre-certified safety Real Time Operating System (RTOS) developed by WHIS, a safety systems company. It delivers superior performance and pre-certified dependability, whilst utilizing minimal resources. It is based on the FreeRTOS functional model, with simple migration possibilities. SAFERTOS is available pre-certified to IEC 61508-3 SIL 3 by TÜV SÜD or pre-certified to ISO 26262 ASIL D by TÜV SÜD.

With an imperceptible boot time, SAFERTOS is an ideal choice in systems that need to protect users and equipment from hazards quickly after a power on or brown out event.

SAFERTOS provides deterministic event handling, frequently used in motor control applications requiring precision control. It is the ideal choice for systems that need to respond quickly to safety events, where the system must be placed into a safe state in the shortest possible time.

It is common to reduce the power consumed by the processor by using the idle Task hook to place the processor into a low power state. The power saving that can be achieved by this simple method varies depending on CPU utilisation but is limited by the necessity to periodically exit and then re-enter the low power state to process RTOS tick interrupts.

Alternatively, when supported by the processor, SAFERTOS can be purchased supporting a tickless Ultra-Low Power Mode. Here power is saved by completely stopping the RTOS tick interrupt during idle periods and placing the system in a power saving mode. Stopping the tick interrupt allows the processor to remain in a deep power saving mode longer until either an interrupt occurs, or it is time for the RTOS to re-activate a Task.

An RTOS that undertakes dynamic memory allocation can introduce a significant risk into a safety critical system. What happens when the RTOS needs to allocate more memory to execute a safety Task, but no more memory exists?

SAFERTOS does not perform any dynamic memory allocation operations, but instead requires the application to allocate a block of memory for SAFERTOS during the initialisation sequence. Reference to this memory block is passed to SAFERTOS via the API during the initialisation phase. Application designers are still able to use dynamic memory allocation within their designs.

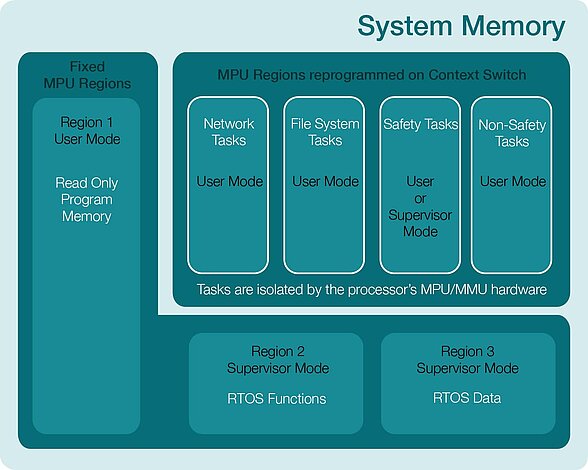

SAFERTOS supports the definition and manipulation of MPU regions on a per task basis. This feature provides the tools allowing developers to add a degree of spatial separation between tasks, which used effectively, can help prevent tasks directly making unintentional or accidental access to incorrect memory regions.

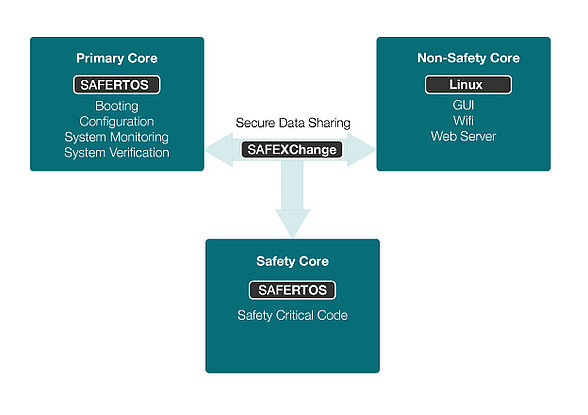

SAFERTOS is ideally suited for use on the booting core of a multi-core/multi processor safety system. SAFERTOS can quickly and effectively bring the system up, configure the safety partitions and execute critical safety functionality before enabling other cores/processors, that could run non-critical applications such as Linux to implement web servers and WiFi connections.

In a multicore environment, SAFERTOSis typically used on cores implementing safety critical functionality, or on cores providing monitoring/verification of the primary function. Due to its high safety classification, SAFERTOS can safely be used on both primary and monitoring cores, removing the need to use differential software.

Format: online training

Duration: 2 days, from 9:00 a.m. to 1 p.m.

Language of instruction: German (presentation slides in English)

Costs: 650.00 EUR (early bird discount 100 EUR)